History

- 8086 Microprocessor was designed by Intel in 1976.

Introduction

- 8086 Microprocessor is an enhanced version of 8085.

- 8086 is available in 3 stable versions based on the frequency of operation(processing speed) −

- 5MHz

- 8MHz

- 10 MHz

Features

-

It is a 16-bit Microprocessor having 20-bit address lines and 16-bit data lines that provides up to 1MB storage. In other words, it was the first 16-bit processor having 16-bit ALU, 16-bit registers, internal data bus, and 16-bit external data bus resulting in faster processing.

- It can directly address up to 220 = 1 Mbyte of memory.

-

It has an instruction queue, which is capable of storing six instruction bytes from the memory resulting in faster processing.

-

It uses two stages of pipelining, i.e. Fetch Stage and then Execute Stage, which improves performance. Fetch stage can prefetch up to 6 bytes of instructions and stores them in the queue. Execute stage executes these instructions.

-

It has 256 vectored interrupts.

-

It consists of 29,000 transistors.

- It is general purpose register based processor.

-

It supports two modes of operation, i.e. Maximum mode and Minimum mode. Maximum mode is suitable for system having multiple processors and Minimum mode is suitable for system having a single processor.

Architecture

- It consists of powerful instruction set, which provides operations like multiplication and division easily.

- Intel 8086 is built on a single semiconductor chip and packaged in a 40-pin IC package. The type of package is DIP (Dual Inline Package).

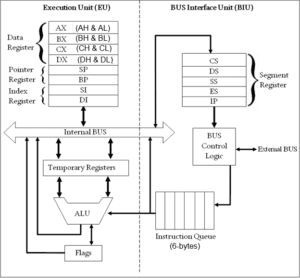

- 8086 microprocessor typically consists of two independent functional units: a Bus Interface Unit (BIU) and an Execution Unit (EU).

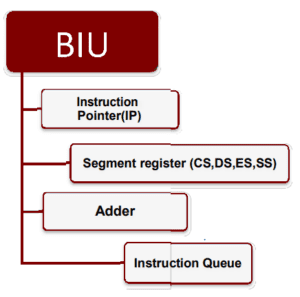

- Bus Interface Unit (BIU) :-

- Performs transfer of data and addresses using buses.

- Fetches instruction codes, stores fetched instruction codes in first-in-first-out register set called Instruction queue.

- Reads data from memory and I/O devices.

- Writes data to memory and I/O devices.

- Relocates addresses of operands since it gets un-relocated operand addresses from EU. The EU tells the BIU from where to fetch instructions or where to read data.

- The BIU part of CPU performs all bus operations such as instruction fetching, reading and writing operands for memory and calculating the addresses of the memory operands.

- The bus interface unit is responsible for performing all external bus operations.

- The BIU uses a mechanism known as an instruction queue to implement pipeline architecture. The instruction bytes are transferred to the instruction queue. This queue permits prefetch of up to six bytes of instruction code. Whenever the queue of the BIU is not full and it has room for at least two more bytes and at the same time EU is not requesting it to read or write operands from memory, the BIU is free to look ahead in the program by prefetching the next sequential instruction. These prefetching instructions are held in its FIFO queue.

- With its 16 bit data bus, the BIU fetches two instruction bytes in a single memory cycle. After a byte is loaded at the input end of the queue, it automatically shifts up through the FIFO to the empty location nearest the output. Finally, the EU accesses the queue from the output end. It reads one instruction byte after the other from the output of the queue. If the queue is full and the EU is not requesting access to operand in memory.

- The BIU also contains a dedicated adder combinational circuit which is used to generate the 20 bit physical address that is output on the address bus. This address is formed by adding an appended 16 bit segment address and a 16 bit offset address.

- It provides a full 16 bit bidirectional data bus and 20 bit address bus.

- The BIU unit performs Instruction fetch , Instruction queuing, Operand fetch and storage, Address calculation relocation and Bus control.

- BIU possess Segment register, Instruction pointer register etc.

- The BIU fetches instructions using the CS and IP, Data is fetched using a segment register (usually the DS) and an effective address (EA) computed by the EU depending on the addressing mode.

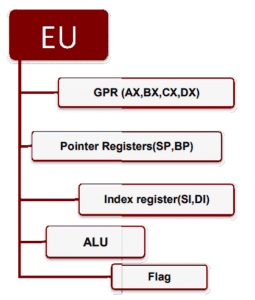

- Execution Unit(EU) :-

- General purpose registers, stack pointer, base pointer and index registers, ALU, flag registers (FLAGS), instruction decoder and timing and control unit constitute the major parts of execution unit (EU).

- The EU receives opcode of an instruction from the instruction queue, decodes it and then executes it. At the same time, the BIU fetches next instruction codes from the memory and stores them in the instruction queue.

- The BIU and EU operate in parallel independently, hence processing becomes faster.

- The Execution unit is responsible for decoding and executing all the instructions.

- The EU extracts instructions from the top of the queue in the BIU, decodes them, generates operands if necessary, passes them to the BIU and requests it to perform the read or write bus cycles to memory or I/O and perform the operation specified by the instruction on the operands.

- During the execution of the instruction, the EU tests the status and control flags and updates them based on the results of executing the instruction.

- If the queue is empty, the EU waits for the next instruction byte to be fetched and shifted to top of the queue.

- When the EU executes a branch or jump instruction, it transfers control to a location corresponding to another set of sequential instructions.

- EU possess Data Registers, Segment Registers, Address Registers, Flag Registers etc. in their structure.

- The BIU and EU part of CPU include three main or basic functional units or components:-

- Bus Interface Unit (BIU) :-

(A) Register Organisation

-

-

- It has a set of registers for holding data in the form of binary information.

-

(B) Arithmetic and Logic Unit (ALU) Organisation

-

-

- This structure performs data manipulation(processing)

-

(C) Control Unit (CU) Organisation

-

-

- This structure coordinates and controls the various operations and initiates the appropriate sequence of micro-operations for each task.

- Computer instructions are normally stored in consecutive memory locations and are executed in sequence one by one.

- The control unit allows reading of an instruction from a specific address in memory and executes it with the help of ALU and Register.

-

![]()

0 Comments